Supóngase que en ambas terminales de entrada A y B se aplica el equivalente eléctrico de un cero ("0") lógico, lo cual equivale a tener "aterrizadas" ambas entradas al punto de referencia conocido como "tierra eléctrica". Entonces cada uno de los transistores MOS estará en estado de "encendido" (ON) o "apagado" (OFF) de la siguiente manera:

Como puede verse, los dos transistores MOS superiores Q1 y Q2 que están conectados en paralelo estarán ambos "encendidos", con lo cual la salida Output del circuito estará conectada directamente a la fuente de voltaje Vdd, la cuyo valor tomaremos como el "1" lógico, mientras que los transistores MOS Q3 y Q4 que están amboso conectados en serie estarán ambos "apagados", pudiendo ser considerados ambos en tal caso como un circuito abierto que no conducirá corriente alguna. En este caso, con dos entradas de "0" tendremos que la salida será "1".

Veamos ahora el caso en que en aplicamos un "0" lógico en la terminal de entrada A y un "1" lógico en la terminal de entrada B:

En este caso, el transistor Q1 estará encendido (ON), con capacidad para poder conducir corriente, razón por la cual se le puede considerar como un "corto circuito" que sirve para conectar la salida al voltaje de la fuente Vdd, o sea al "1" lógico, mientras que el transistor Q2 estará apagado (OFF), pudiendo ser considerado eléctricamente como un circuito abierto. Y aunque el transistor Q4 también está en la condición de "encendido" estando por lo tanto en la capacidad para poder conducir corriente, el transistor Q2 con el cual está conectado en serie está en la condición de apagado (OFF), de modo tal que no hay posibilidad alguna de conducción de corriente a través de la combinación en serie de Q3 y Q4. En este caso, tenemos que con una entrada de "0" en la terminal A y una entrada de "1" en la terminal B la salida será "1".

La situación en la que aplicamos una entrada de "1" en la terminal A y una entrada de "0" en la terminal B no es muy diferente a la situación anterior:

y seguiremos teniendo un "1" a la salida del circuito.

Por último, cuando aplicamos un "1" lógico en ambas entradas A y B:

podemos ver que la combinación paralela de los transistores Q1 y Q2 estará en la condición de "apagado" (OFF), desconectando a la salida Output de la fuente de poder Vdd, mientras que por el otro lado la combinación en serie de ambos transistores Q3 y Q4 estará en la condición de "encendido" (ON), conectando eléctricamente la salida Output a "tierra eléctrica". Este es un circuito cuya salida será "0" únicamente cuando ambas entradas son "1", y es por lo tanto un circuito NAND.

La construcción de una compuerta lógica NOR mediante la tecnología de transistores MOS complementarios no es muy diferente a la de la compuerta lógica NAND, como podemos apreciarlo en el siguiente diagrama del circuito:

Como puede verse, las únicas diferencias son que mientras los transistores Q1 y Q2 en el circuito NAND estaban conectados en paralelo, ahora en el circuito NOR están conectados en serie, mientras que los transistores Q3 y Q4 que estaban conectados en serie ahora están conectados en paralelo. El procedimiendo de análisis que se llevó a cabo sobre el circuito CMOS NAND es casi idéntico al procedimiento de análisis que se lleva a cabo sobre el circuito CMOS NOR.

Con los componentes lógicos basados en la tecnología CMOS, podemos construír una compuerta AND con el simple hecho de conectar un inversor NOT a la salida de un bloque AND:

Existe disponible en Internet un programa interactivo muy instructivo y entretenido mantenido por el Profesor Norman Hendrich de la Universidad de Hamburg (Alemania) que demuestra la acción de los transistores CMOS empezando por el funcionamiento de los transistores MOS hasta cubrir algunas compuertas básicas NAND e inclusive hasta un flip-flop D construído con transistores MOS complementarios. La dirección para accesar estos programas interactivos (los cuales requieren que la computara tenga instalada la plataforma Java 1.0, obtenible gratuitamente de Internet):

http://tams-www.informatik.uni-hamburg.de/applets/cmos/cmosdemo.html

La forma en la cual trabajan los applets colocados en esta página es la siguiente:

(1) En la demostración "CMOS transistor demo", si pulsamos con el mouse de la computadora en la terminal de entrada G del transistor tipo-P, el color de la terminal cambiará repetidamente de azul (el estado "0") a rojo (el estado "1") y viceversa. Con la terminal G de color azul (un "0" a la entrada) ambas terminales del transistor toman el mismo color rojo, y el transistor está conduciendo, mientras que si la terminal G toma el color rojo el transistor se "abre" y deja de conducir. La acción es similar en el transistor tipo-N de la derecha.

(2) En la demostración "CMOS inverter demo", si pulsamos repetidamente con el mouse de la computadora en la terminal de entrada A de la configuración complementaria de transistores, el color de la terminal cambiará repetidamente de rojo (un "1" a la entrada) a azul (un "0" a la entrada) y a amarillo (sin conexión ni a "1" ni a "0", lo que llamamos comúnmente un estado flotante, equivalente a cortar con unas pinzas el alambre que va a la termina A). Esta demostración ilustra algo importante a lo cual no le habíamos dado tanta importancia anteriormente con el fin de no atiborrar a los lectores con un exceso de detalles: estrictamente hablando, la ausencia de un voltaje no es lo mismo que el equivalente de un "0" lógico. En realidad, al hablar de poner un "0" a la entrada de la terminal G de un transistor MOS (o de cualquier compuerta lógica bajo cualquier familia de circuitos integrados, la que sea), por la ausencia de un voltaje no se está queriendo dar a entender en ningún momento que la terminal de entrada es desconectada totalmente y por completo del circuito; tal estado es un estado altamente inestable. Siempre que se habla de poner un "0" en una entrada se debe entender que la terminal se debe conectar al polo negativo de la fuente de poder y nunca que se está desconectando eléctricamente del resto del sistema. La buena práctica del diseño de los circuitos lógicos exige siempre que todas las entradas a una compuerta o a un bloque estén conectadas siempre eléctricamente al sistema, por ningún motivo deben quedar "flotantes". Por esto mismo, todas las entradas no-utilizadas en un circuito integrado deben ser conectadas eléctricamente a "tierra".

(3) En la demostración "CMOS inverter power consumption demo", se puede ver cómo el consumo de energía de una configuración CMOS ocurre cuando la entrada está cambiando de un estado estable al otro, precisamente en ese breve lapso de tiempo en el cual la entrada tiene un color amarillo.

(4) La demostración "CMOS 2-input NOR gate demo" ilustra claramente cómo en una compuerta NOR de dos entradas la salida va ciclando según los valores de las entradas A y B sean "1" o "0". Esta demostración refuerza el concepto destacando en la Tabla de Verdad anexa el estado correspondiente a las entradas seleccionadas.

(5) La demostración "CMOS 2-input NAND gate demo" ilustra claramente cómo en una compuerta NAND de dos entradas la salida va ciclando según los valores de las entradas A y B sean "1" o "0". Al igual que en el caso anterior, esta demostración también refuerza el concepto destacando en la Tabla de Verdad anexa el estado correspondiente a las entradas seleccionadas.

(6) La demostración "CMOS 3-input NAND gate demo" ilustra claramente cómo en una compuerta NAND de tres entradas la salida va ciclando según los valores de las entradas A, B y C sean "1" o "0".

(7) La demostración "CMOS complex AOI32 (and-or-invert) gate demo" es precisamente la implementación con tecnología CMOS de la famosa configuración AOI que vimos en la Sección Capítulo 3: Problemas Resueltos.

(8) La demostración "CMOS transmision gate demo" demuestra la forma en la cual se pueden interconectar los transistores MOS para poder obtener lo que aquí llaman una compuerta de transmisión o compuerta-T (T-gate), que permite conectar eléctricamente la entrada a la salida permitiendo el paso de la señal en ambas direcciones. En realidad, esto es lo mismo que habíamos visto en el Capítulo 7 del libro (Tópicos Especiales), a lo cual llamamos interruptor bilateral.

(9) La demostración "CMOS D-latch gate demo" demuestra cómo se puede construír con las compuertas de transmisión vistas arriba y con pares de transistores complementarios MOS un bloque de acción similar a la del flip-flop tipo-D para almacenar un bit de información.

Se pueden encontrar detalles adicionales sobre la familia CMOS de la famosa serie-4000 en la página de la Wikipedia:

http://en.wikipedia.org/wiki/4000_series

También podemos encontrar en Wikipedia un listado de los circuitos integrados que pertenecen a esta familia yéndonos al siguiente enlace:

http://en.wikipedia.org/wiki/List_of_4000_series_integrated_circuits

Los transistores complementarios CMOS nos permiten construír fácilmente, además de las funciones lógicas básicas cubiertas arriba, otras funciones "clásicas", tales como el bloque OAI (Or-And-Invert):

Este bloque es la contraparte del bloque AOI (And-Or-Invert) introducido en la sección de problemas resueltos correspondiente al capítulo 3 (El álgebra Boleana).

La tecnología de los transistores MOS es utilizada no sólo como punto de partida para construír funciones lógicas básicas, también sirve para construír las memorias de acceso aleatorio RAM requeridas por cualquier computadora digital para poder funcionar. Existen dos tipos de memorias RAM disponibles bajo esta tecnología:

1) Las memorias RAM estáticas (SRAM, static RAM).

2) Las memorias RAM dinámicas (DRAM, dynamic RAM).

La "célula básica" del RAM estático, basada en una configuración de transistores MOS que funcionalmente reproduce la acción de un flip-flop como elemento de memoria, y utilizada para almacenar un "bit" de información dentro de este flip-flop, es la siguiente:

El flip-flop de almacenamiento está bosquejado dentro de la región amarilla del diagrama. En el diagrama se recuerda que un voltaje bajo (un "0") apaga el transistor NMOS y enciende el transistor PMOS, mientras que un voltaje alto (un "1") enciende al transistor NMOS y apaga al transistor PMOS. Como es típico en cualquier configuración moderna de RAMs, tenemos una línea para situar a la célula básica dentro de una serie de renglones (ROW LINE) y otra línea perpendicular para situarla dentro de una serie de columnas (COLUMN LINE). El flip-flop es puesto en el estado "0" ó en el estado "1" poniendo un voltaje en la línea del renglón que corresponde a la célula seleccionada y aplicando voltajes contrarios en las dos líneas de columna que identifica a la célula.

Como suele suceder, muchas veces la solución "teórica" a un problema no necesariamente es la más económica ni la más obvia. Aunque podemos construír una célula básica para un RAM partiendo exclusivamente del uso piramidal de funciones lógicas básicas, existe una forma más económica de almacenar un "bit" de información dentro de una célula básica que no requiere de configuración alguna de flip-flop. Esta consiste en utilizar un pequeño condensador eléctrico microminiaturizado para almacenar una carga eléctrica, de modo tal que la presencia de una carga eléctrica almacenada en la célula básica nos indique la presencia de un "1" lógico mientras que la ausencia de una carga eléctrica nos indicará un "0" lógico. Desafortunadamente, ningún condensador eléctrico por bueno que sea puede retener la carga almacenada por tiempo indefinido, y en una memoria construída de esta manera es necesario estar "refrescando" la célula continuamente de manera dinámica para evitar perder la información. También al leer un "1" es necesario volver a refrescar el almacenamiento del "1" con el fin de evitar perder ese bit de información. Es por esta razón que este tipo de memorias RAM son conocidas como memorias RAM dinámicas.

La "célula básica" del RAM dinámico utilizada para almacenar un "bit" de información es la siguiente:

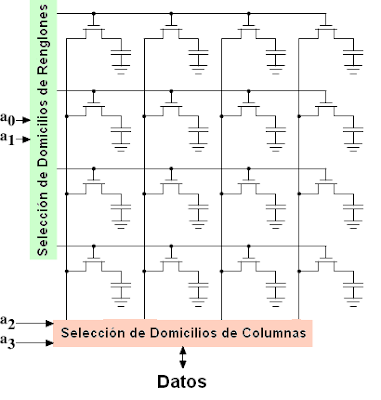

Como es típico en la microelectrónica, la reproducción "fotográfica" miniaturizada de esta célula básica nos permite construír una memoria RAM con capacidad para varios bits como la siguiente memoria RAM dinámica en la que podemos almacenar 16 bits seleccionables cada uno de ellos con el domicilio compuesto a3a2a1a0:

1 comentario:

Que buena informacion, que lindo haber topado con tremendo post, felicitaciones !

Publicar un comentario