Exponsor

CURSO TÉCNICO INSTALADOR DE ENERGÍA SOLAR TÉRMICA

jueves, 9 de abril de 2009

SISTEMAS ELECTRÓNICOS

Entradas o Inputs – Sensores (o transductores) electrónicos o mecánicos que toman las señales (en forma de temperatura, presión, etc.) del mundo físico y las convierten en señales de corriente o voltaje. Ejemplo: El termopar, la foto resistencia para medir la intensidad de la luz, etc.

Circuitos de procesamiento de señales – Consisten en piezas electrónicas conectadas juntas para manipular, interpretar y transformar las señales de voltaje y corriente provenientes de los transductores.

Salidas o Outputs – Actuadores u otros dispositivos (también transductores) que convierten las señales de corriente o voltaje en señales físicamente útiles. Por ejemplo: un display que nos registre la temperatura, un foco o sistema de luces que se encienda automáticamente cuando este obscureciendo.

Básicamente son tres etapas: La primera (transductor), la segunda (circuito procesador) y la tercera (circuito actuador).

Como ejemplo supongamos un televisor. Su entrada es una señal de difusión recibida por una antena o por un cable. Los circuitos de procesado de señales del interior del televisor extraen la información sobre el brillo, el color y el sonido de esta señal. Los dispositivos de salida son un tubo de rayos catódicos que convierte las señales electrónicas en imágenes visibles en una pantalla y unos altavoces. Otro ejemplo puede ser el de un circuito que ponga de manifiesto la temperatura de un proceso, el transductor puede ser un termocouple, el circuito de procesamiento se encarga de convertir la señal de entrada en un nivel de voltaje (comparador de voltaje o de ventana) en un nivel apropiado y mandar la información decodificándola a un display donde nos dé la temperatura real y si esta excede un límite preprogramado activar un sistema de alarma (circuito actuador) para tomar las medida pertinentes.

LAS FAMILIAS LÓGICAS ( III )

Supóngase que en ambas terminales de entrada A y B se aplica el equivalente eléctrico de un cero ("0") lógico, lo cual equivale a tener "aterrizadas" ambas entradas al punto de referencia conocido como "tierra eléctrica". Entonces cada uno de los transistores MOS estará en estado de "encendido" (ON) o "apagado" (OFF) de la siguiente manera:

Como puede verse, los dos transistores MOS superiores Q1 y Q2 que están conectados en paralelo estarán ambos "encendidos", con lo cual la salida Output del circuito estará conectada directamente a la fuente de voltaje Vdd, la cuyo valor tomaremos como el "1" lógico, mientras que los transistores MOS Q3 y Q4 que están amboso conectados en serie estarán ambos "apagados", pudiendo ser considerados ambos en tal caso como un circuito abierto que no conducirá corriente alguna. En este caso, con dos entradas de "0" tendremos que la salida será "1".

Veamos ahora el caso en que en aplicamos un "0" lógico en la terminal de entrada A y un "1" lógico en la terminal de entrada B:

En este caso, el transistor Q1 estará encendido (ON), con capacidad para poder conducir corriente, razón por la cual se le puede considerar como un "corto circuito" que sirve para conectar la salida al voltaje de la fuente Vdd, o sea al "1" lógico, mientras que el transistor Q2 estará apagado (OFF), pudiendo ser considerado eléctricamente como un circuito abierto. Y aunque el transistor Q4 también está en la condición de "encendido" estando por lo tanto en la capacidad para poder conducir corriente, el transistor Q2 con el cual está conectado en serie está en la condición de apagado (OFF), de modo tal que no hay posibilidad alguna de conducción de corriente a través de la combinación en serie de Q3 y Q4. En este caso, tenemos que con una entrada de "0" en la terminal A y una entrada de "1" en la terminal B la salida será "1".

La situación en la que aplicamos una entrada de "1" en la terminal A y una entrada de "0" en la terminal B no es muy diferente a la situación anterior:

y seguiremos teniendo un "1" a la salida del circuito.

Por último, cuando aplicamos un "1" lógico en ambas entradas A y B:

podemos ver que la combinación paralela de los transistores Q1 y Q2 estará en la condición de "apagado" (OFF), desconectando a la salida Output de la fuente de poder Vdd, mientras que por el otro lado la combinación en serie de ambos transistores Q3 y Q4 estará en la condición de "encendido" (ON), conectando eléctricamente la salida Output a "tierra eléctrica". Este es un circuito cuya salida será "0" únicamente cuando ambas entradas son "1", y es por lo tanto un circuito NAND.

La construcción de una compuerta lógica NOR mediante la tecnología de transistores MOS complementarios no es muy diferente a la de la compuerta lógica NAND, como podemos apreciarlo en el siguiente diagrama del circuito:

Como puede verse, las únicas diferencias son que mientras los transistores Q1 y Q2 en el circuito NAND estaban conectados en paralelo, ahora en el circuito NOR están conectados en serie, mientras que los transistores Q3 y Q4 que estaban conectados en serie ahora están conectados en paralelo. El procedimiendo de análisis que se llevó a cabo sobre el circuito CMOS NAND es casi idéntico al procedimiento de análisis que se lleva a cabo sobre el circuito CMOS NOR.

Con los componentes lógicos basados en la tecnología CMOS, podemos construír una compuerta AND con el simple hecho de conectar un inversor NOT a la salida de un bloque AND:

Existe disponible en Internet un programa interactivo muy instructivo y entretenido mantenido por el Profesor Norman Hendrich de la Universidad de Hamburg (Alemania) que demuestra la acción de los transistores CMOS empezando por el funcionamiento de los transistores MOS hasta cubrir algunas compuertas básicas NAND e inclusive hasta un flip-flop D construído con transistores MOS complementarios. La dirección para accesar estos programas interactivos (los cuales requieren que la computara tenga instalada la plataforma Java 1.0, obtenible gratuitamente de Internet):

http://tams-www.informatik.uni-hamburg.de/applets/cmos/cmosdemo.html

La forma en la cual trabajan los applets colocados en esta página es la siguiente:

(1) En la demostración "CMOS transistor demo", si pulsamos con el mouse de la computadora en la terminal de entrada G del transistor tipo-P, el color de la terminal cambiará repetidamente de azul (el estado "0") a rojo (el estado "1") y viceversa. Con la terminal G de color azul (un "0" a la entrada) ambas terminales del transistor toman el mismo color rojo, y el transistor está conduciendo, mientras que si la terminal G toma el color rojo el transistor se "abre" y deja de conducir. La acción es similar en el transistor tipo-N de la derecha.

(2) En la demostración "CMOS inverter demo", si pulsamos repetidamente con el mouse de la computadora en la terminal de entrada A de la configuración complementaria de transistores, el color de la terminal cambiará repetidamente de rojo (un "1" a la entrada) a azul (un "0" a la entrada) y a amarillo (sin conexión ni a "1" ni a "0", lo que llamamos comúnmente un estado flotante, equivalente a cortar con unas pinzas el alambre que va a la termina A). Esta demostración ilustra algo importante a lo cual no le habíamos dado tanta importancia anteriormente con el fin de no atiborrar a los lectores con un exceso de detalles: estrictamente hablando, la ausencia de un voltaje no es lo mismo que el equivalente de un "0" lógico. En realidad, al hablar de poner un "0" a la entrada de la terminal G de un transistor MOS (o de cualquier compuerta lógica bajo cualquier familia de circuitos integrados, la que sea), por la ausencia de un voltaje no se está queriendo dar a entender en ningún momento que la terminal de entrada es desconectada totalmente y por completo del circuito; tal estado es un estado altamente inestable. Siempre que se habla de poner un "0" en una entrada se debe entender que la terminal se debe conectar al polo negativo de la fuente de poder y nunca que se está desconectando eléctricamente del resto del sistema. La buena práctica del diseño de los circuitos lógicos exige siempre que todas las entradas a una compuerta o a un bloque estén conectadas siempre eléctricamente al sistema, por ningún motivo deben quedar "flotantes". Por esto mismo, todas las entradas no-utilizadas en un circuito integrado deben ser conectadas eléctricamente a "tierra".

(3) En la demostración "CMOS inverter power consumption demo", se puede ver cómo el consumo de energía de una configuración CMOS ocurre cuando la entrada está cambiando de un estado estable al otro, precisamente en ese breve lapso de tiempo en el cual la entrada tiene un color amarillo.

(4) La demostración "CMOS 2-input NOR gate demo" ilustra claramente cómo en una compuerta NOR de dos entradas la salida va ciclando según los valores de las entradas A y B sean "1" o "0". Esta demostración refuerza el concepto destacando en la Tabla de Verdad anexa el estado correspondiente a las entradas seleccionadas.

(5) La demostración "CMOS 2-input NAND gate demo" ilustra claramente cómo en una compuerta NAND de dos entradas la salida va ciclando según los valores de las entradas A y B sean "1" o "0". Al igual que en el caso anterior, esta demostración también refuerza el concepto destacando en la Tabla de Verdad anexa el estado correspondiente a las entradas seleccionadas.

(6) La demostración "CMOS 3-input NAND gate demo" ilustra claramente cómo en una compuerta NAND de tres entradas la salida va ciclando según los valores de las entradas A, B y C sean "1" o "0".

(7) La demostración "CMOS complex AOI32 (and-or-invert) gate demo" es precisamente la implementación con tecnología CMOS de la famosa configuración AOI que vimos en la Sección Capítulo 3: Problemas Resueltos.

(8) La demostración "CMOS transmision gate demo" demuestra la forma en la cual se pueden interconectar los transistores MOS para poder obtener lo que aquí llaman una compuerta de transmisión o compuerta-T (T-gate), que permite conectar eléctricamente la entrada a la salida permitiendo el paso de la señal en ambas direcciones. En realidad, esto es lo mismo que habíamos visto en el Capítulo 7 del libro (Tópicos Especiales), a lo cual llamamos interruptor bilateral.

(9) La demostración "CMOS D-latch gate demo" demuestra cómo se puede construír con las compuertas de transmisión vistas arriba y con pares de transistores complementarios MOS un bloque de acción similar a la del flip-flop tipo-D para almacenar un bit de información.

Se pueden encontrar detalles adicionales sobre la familia CMOS de la famosa serie-4000 en la página de la Wikipedia:

http://en.wikipedia.org/wiki/4000_series

También podemos encontrar en Wikipedia un listado de los circuitos integrados que pertenecen a esta familia yéndonos al siguiente enlace:

http://en.wikipedia.org/wiki/List_of_4000_series_integrated_circuits

Los transistores complementarios CMOS nos permiten construír fácilmente, además de las funciones lógicas básicas cubiertas arriba, otras funciones "clásicas", tales como el bloque OAI (Or-And-Invert):

Este bloque es la contraparte del bloque AOI (And-Or-Invert) introducido en la sección de problemas resueltos correspondiente al capítulo 3 (El álgebra Boleana).

La tecnología de los transistores MOS es utilizada no sólo como punto de partida para construír funciones lógicas básicas, también sirve para construír las memorias de acceso aleatorio RAM requeridas por cualquier computadora digital para poder funcionar. Existen dos tipos de memorias RAM disponibles bajo esta tecnología:

1) Las memorias RAM estáticas (SRAM, static RAM).

2) Las memorias RAM dinámicas (DRAM, dynamic RAM).

La "célula básica" del RAM estático, basada en una configuración de transistores MOS que funcionalmente reproduce la acción de un flip-flop como elemento de memoria, y utilizada para almacenar un "bit" de información dentro de este flip-flop, es la siguiente:

El flip-flop de almacenamiento está bosquejado dentro de la región amarilla del diagrama. En el diagrama se recuerda que un voltaje bajo (un "0") apaga el transistor NMOS y enciende el transistor PMOS, mientras que un voltaje alto (un "1") enciende al transistor NMOS y apaga al transistor PMOS. Como es típico en cualquier configuración moderna de RAMs, tenemos una línea para situar a la célula básica dentro de una serie de renglones (ROW LINE) y otra línea perpendicular para situarla dentro de una serie de columnas (COLUMN LINE). El flip-flop es puesto en el estado "0" ó en el estado "1" poniendo un voltaje en la línea del renglón que corresponde a la célula seleccionada y aplicando voltajes contrarios en las dos líneas de columna que identifica a la célula.

Como suele suceder, muchas veces la solución "teórica" a un problema no necesariamente es la más económica ni la más obvia. Aunque podemos construír una célula básica para un RAM partiendo exclusivamente del uso piramidal de funciones lógicas básicas, existe una forma más económica de almacenar un "bit" de información dentro de una célula básica que no requiere de configuración alguna de flip-flop. Esta consiste en utilizar un pequeño condensador eléctrico microminiaturizado para almacenar una carga eléctrica, de modo tal que la presencia de una carga eléctrica almacenada en la célula básica nos indique la presencia de un "1" lógico mientras que la ausencia de una carga eléctrica nos indicará un "0" lógico. Desafortunadamente, ningún condensador eléctrico por bueno que sea puede retener la carga almacenada por tiempo indefinido, y en una memoria construída de esta manera es necesario estar "refrescando" la célula continuamente de manera dinámica para evitar perder la información. También al leer un "1" es necesario volver a refrescar el almacenamiento del "1" con el fin de evitar perder ese bit de información. Es por esta razón que este tipo de memorias RAM son conocidas como memorias RAM dinámicas.

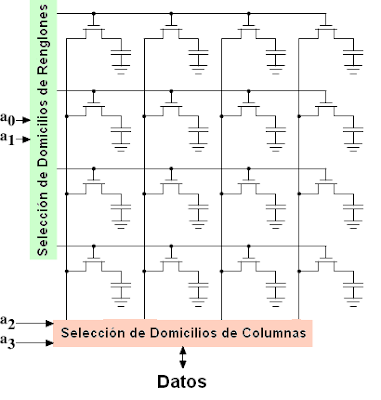

La "célula básica" del RAM dinámico utilizada para almacenar un "bit" de información es la siguiente:

Como es típico en la microelectrónica, la reproducción "fotográfica" miniaturizada de esta célula básica nos permite construír una memoria RAM con capacidad para varios bits como la siguiente memoria RAM dinámica en la que podemos almacenar 16 bits seleccionables cada uno de ellos con el domicilio compuesto a3a2a1a0:

LAS FAMILIAS LÓGICAS ( II )

La siguiente figura muestra cómo está montada dentro de estos encapsulamientos de plástico DIP la "pastilla de silicón" o wafer:

Se puede encontrar una descripción más a fondo sobre esta tecnología en el siguiente enlace:

http://en.wikipedia.org/wiki/7400

Aunque la familia TTL en cierta forma ya está algo obsoleta, superada por las familias CMOS, los circuitos integrados TTL fueron tan utilizados que aún hay muchos de ellos en operación. Podemos encontrar en Wikipedia un listado de los circuitos integrados que pertenecen a esta familia yéndonos al siguiente enlace:

http://en.wikipedia.org/wiki/List_of_7400_series_integrated_circuits

La familia Schottky TTL

Un paso posterior en la evolución de la familia TTL fue la implementación en los circuitos integrados de la misma de diodos basados en el diodo Schottky, el cual es representado en los diagramas esquemáticos con el siguiente símbolo:

y el cual permitió incrementar de forma considerable la rapidez con la cual los circuitos integrados podían llevar a cabo sus operaciones. La identificación de un circuito integrado de la familia Schottky TTL es la misma que la utilizada por la familia TTL, excepto que para denotar su mayor velocidad se le agrega una "S" intermedia a la nomenclatura de cada componente de la familia. De este modo, el equivalente pin-por-pin del circuito integrado 7400 vendría siendo el circuito integrado 74S00, que a su vez vendría siendo el bloque fundamental de esta familia. La nomenclatura se mantiene constante a través de todos los componentes de esta familia. Por ejemplo, en el circuito integrado 74S32, los primeros dos dígitos "74" indican que es un circuito integrado correspondiente a la familia TTL, los últimos dos dígitos "32" indican que se trata de un paquete que incluye cuatro compuertas OR de dos entradas cada una, y la letra "S" intermedia indica que se trata de un circuito integrado de alta velocidad.

La familia CMOS

Así como Texas Instruments se convirtió en una empresa pionera al introducir la familia lógica basada en la tecnología TTL, también la empresa RCA llevó a cabo el siguiente proceso evolutivo introduciendo como una alternativa a la familia TTL una serie de circuitos integrados basados en una tecnología que requiere un consumo muy bajo de energía: la familia CMOS (Complementary Metal-Oxide-Semiconductor). El acrónimo indica que para la construcción de estos circuitos se utiliza ya no el transistor bipolar sino el transistor MOS basado a su vez en el transistor de efecto de campo (field effect transistor), apareado en pares de modo tal que puedan implementar una de varias compuertas lógícas de las maneras que veremos a continuación. La gran ventaja de este tipo de componentes es que presentan una alta impedancia (resistencia eléctrica) de entrada consumiendo por lo tanto muy poca corriente eléctrica. El bajo consumo de corriente eléctrica hace a esta tecnología atractiva en aplicaciones en las cuales es imperativo el ahorro de energía (principalmente artículos electrónicos operados con batería portátil desechable). Sin embargo, su velocidad es inferior a la velocidad de la familia TTL, de modo tal que cada familia tiene aquí sus pros y sus contras.

Por la forma en la cual está integrada la electrónica interna, el "bloque fundamental" de la familia CMOS no es tampoco ninguna de nuestras funciones lógicas básicas (OR, AND, NOT), sino, al igual que en el caso de la familia RTL, puede ser ya sea la función NOR o también la función NAND. El circuito integrado básico de la gran familia progenitora de las compuertas lógicas CMOS es el 4000, basado en los bloques NOR, cuya relación de pins es la siguiente:

A continuación tenemos el "diagrama esquemático" de las funciones proporcionadas por otros de los circuitos lógicos pertenecientes a esta familia:

La tecnología CMOS se ha vuelto tan importante, que no podemos cerrar este Suplemento sin dar una idea así sea generalizada sobre cómo trabaja la electrónica CMOS, para beneficio de los lectores que tengan algunas nociones elementales sobre cuestiones eléctricas.

El punto de partida para poder construír compuertas lógicas mediante tecnología CMOS es la física del funcionamiento del transistor MOSFET (acrónimo del inglés Metal Oxide Semiconductor Field Effect Transistor, que en español significa "Transistor de Efecto de Campo Metal Oxido Semiconductor) ejemplificado en los siguientes diagramas en los cuales la región de color amarillo es la capa "metálica", la región de color verde es la región de "óxido" y la región de color magenta es el substrato del semiconductor:

El transistor MOS básico es un componente de tres terminales, dos terminales denominadas D (de la palabra inglesa drain que significa drenaje) y S (de la palabra inglesa source que significa fuente) en las cuales se aplica una fuente de voltaje, y una terminal de "control" denominada G (de la palabra inglesa gate que puede tomarse como gatillo o compuerta). Como puede verse en el diagrama de la izquierda, cuando la terminal G está abierta (Open) sin que se le esté aplicando voltaje alguno, entonces la corriente eléctrica que está tratando de enviar el polo positivo de la batería (resaltada en la trayectoria incompleta de color azul) llega hasta la región (de color ciano) denominada N en donde la posible conducción de corriente eléctrica queda detenida al no haber en la región P (de color magenta) camino alguno mediante el cual se pueda completar la trayectoria. La situación cambia por completo cuando en el diagrama de la derecha le aplicamos un voltaje a la terminal G. Al aplicar dicho voltaje, se polarizan las regiones de color amarillo, verde y magenta, de modo tal que mientras en la región de color amarillo se crean cargas eléctricas positivas en la región P de color magenta (que llamaremos el substrato) se crea una contraparte de igual número de cargas eléctricas negativas, formando dentro de la región P un "canal" N de color azul que conecta las dos regiones N, con lo cual se establece un camino para la conducción de energía eléctrica (resaltada en la trayectoria cerrada de color rojo).

El transistor MOSFET cuyo funcionamiento acabamos de ver es un transistor de tipo canal-N (conocido también como transistor NMOS), así llamado porque el "canal" de conducción que permite el paso de corrientes eléctricas funciona a base de cargas eléctricas negativas. Existe otro transistor MOSFET cuyo funcionamiento es parecido al de arriba excepto que dicho transistor es un transistor MOS de tipo canal-P (conocido también como transistor PMOS) en el cual el "canal" de conducción que permite el paso de corrientes eléctricas funciona a base de cargas eléctricas positivas. En los diagramas esquemáticos es posible distinguir el uno del otro porque el primero de ellos (canal-N) se dibuja utilizando una flecha intermedia entre las terminales D y S que siempre apunta hacia adentro, mientras que en el segundo se dibuja una flecha intermedia que siempre apunta hacia afuera como lo muestra el símbolo empleado para este último:

Aunque no entraremos mucho aquí en los detalles técnicos requeridos en los diseños de circuitos que utilizan transistores de efecto de campo, se hará la observación de que mientras que los modelos teóricos utilizados en el transistor bipolar como el que vimos al principio son modelos basados en corrientes eléctricas (la ganancia beta -ó ß- de un transistor bipolar está especificada como la razón entre la corriente del colector y la corriente de la base del transistor bipolar), los modelos teóricos utilizados en el transistor de efecto de campo son modelos teóricos basados en voltajes eléctricos. La diferencia esencial entre un transistor NMOS y un transistor PMOS es que si al transistor NMOS se le aplica un voltaje equivalente al "1" en la terminal G el transistor se cierra (se pone en el estado ON, equivalente al establecimiento del contacto en un interruptor eléctrico) y si se le remueve dicho voltaje poniendo así un "0" en la terminal G el contacto se abre entrando el transistor en el equivalente al estado OFF en un interruptor eléctrico; mientras que en un transistor PMOS la acción es al revés, si se se le aplica un voltaje equivalente al "1" en la terminal G el transistor se abre entrando el transistor en el equivalente al estado OFF en un interruptor eléctrico, y si se le remueve dicho voltaje poniendo así un "0" en la terminal G el contacto se cierra poniéndose el transistor en el estado ON. Esta acción inversora del transistor PMOS frecuentemente se destaca en los diagramas poniendo la famosa burbuja inversora lógica justo en la terminal G del transistor.

El circuito básico para construír un amplificador de voltajes MOSFET que también puede ser utilizado como inversor lógico siempre y cuando los voltajes de entrada y salida estén restringidos a únicamente dos valores con los cuales se definan el "0" y el "1" es el siguiente para un MOSFET de canal-N:

En este circuito elemental, si se utiliza como inversor lógico, la aplicación de un voltaje Vin en la terminal G ocasiona que el transistor MOSFET comience a conducir, con lo cual toda la caída del voltaje de +5 voltios de la fuente de poder ocurrirá a través de la resistencia de carga Rload de 10 mil ohms cuyo uso limita la magnitud de la corriente eléctrica impidiendo un corto circuito, y el voltaje a través del transistor MOSFET será casi cero. Con este circuito, la aplicación a la entrada de un voltaje de +5 voltios tomado como un "1" lógico produce a la salida un voltaje que podemos tomar como cero voltios, o sea un "0" lógico, mientras que la remoción del voltaje a la entrada que equivale "aterrizar" la entrada a un "0" lógico ocasionará que el transistor MOSFET deje de conducir siendo por lo tanto la salida igual a +5 voltios o un "1" lógico. En pocas palabras, cuando la entrada es "1" la salida es "0", y cuando la entrada es "0" la salida es "1". Esta es precisamente la acción del inversor lógico.

Para un MOSFET de canal-N, el circuito requerido para crear un inversor lógico es el siguiente:

Aunque los dos circuitos anteriores pueden ser utilizados como inversores lógicos, existe un diseño mucho más eficiente que prácticamente no consume nada de corriente eléctrica bajo ninguna circunstancia, un diseño basado en el uso de pares complementarios de transistores MOSFET, uno de tipo-P y uno de tipo-N, de lo cual deriva el uso de la palabra "complementario" en el acrónimo C-MOS o Complementary MOS.

En el siguiente diagrama, tenemos un bosquejo sobre cómo trabaja el circuito CMOS más sencillo de todos, un inversor NOT construído con transistores MOS conectados en serie:

Como puede verse en el diagrama de la izquierda, la aplicación simultánea de un voltaje bajo L (del inglés Low, equivalente al "0" lógico) en las terminales G de ambos transistores MOS hace que el transistor superior PMOS conduzca y que el transistor inferior NMOS se abra, lo cual tiene el efecto de "conectar" la salida al voltaje positivo de la fuente. En pocas palabras, un "0" a la entrada produce un "1" a la salida. Y si se aplica un voltaje alto H (del inglés High, equivalente al "1" lógico) en las terminales G de ambos transistores MOS entonces el transistor superior PMOS se abrirá eléctricamente mientras que el transistor inferior NMOS se "cerrará" conectando la salida al polo negativo de la fuente de poder usualmente denominado como "tierra" o "0". En pocas palabras, un "1" a la entrada produce un "0" a la salida. Esta es precisamente la acción requerida del inversor lógico.

LAS FAMILIAS LÓGICAS ( I )

Posiblemente la manera más sencilla de implementar funciones lógicas sea mediante el uso de diodos, los cuales permiten el paso de la corriente eléctrica en una sola dirección más no en la dirección contraria. Esta manera de construír funciones lógicas es conocida de varias maneras tales como "Diode Logic", "Diode-Diode Logic" o inclusive como "Diode-Resistor Logic".

En el siguiente diagrama esquemático tenemos la función OR implementada con diodos:

El funcionamiento de este circuito es extremadamente sencillo. Si las entradas a los diodos D1 y D2 en las terminales 3 y 4 son "0" (cero voltaje aplicado en ellas) entonces no llegará voltaje alguno a la terminal 1. En pocas palabras, cuando ambas entradas son "0" la salida será "0". Si aplicamos un voltaje (un "1") a la terminal 3 y mantenemos la entrada a la terminal 4 en "0", entonces la corriente eléctrica podrá fluír directamente de la terminal 3 a la terminal 1 poniendo un "1" (el voltaje aplicado en la entrada del diodo D1) en la salida. Esta corriente eléctrica no puede fluír por el diodo D2 aunque su entrada sea "0" porque el diodo solo es capaz de conducir corriente eléctrica en la dirección indicada por la flecha en su símbolo. Con esto, si la entrada en la terminal 3 es "1" y la entrada en la terminal 4 es "0", la salida será "1". Y lo mismo ocurrirá cuando la entrada en la terminal 3 sea "0" y la entrada en la terminal 4 sea "1". En pocas palabras, cuando cualquiera de las entradas es "1" la salida será también "1". Y si ambas entradas son "1" la salida será "1". Esta es precisamente la acción de un OR.

En el siguiente diagrama esquemático tenemos la función AND implementada con diodos:

Este circuito también tiene una explicación sencilla.

Si las entradas a los diodos D1 y D2 en las terminales 4 y 5 son "1", entonces al estar ambos lados de cada diodo al mismo potencial eléctrico ninguno de ellos conducirá corriente eléctrica alguna (la corriente eléctrica sólo puede fluír de un "1" a un "0") y la terminal 1 se mantendrá al mismo nivel del voltaje al cual está conectada a través de la resistencia R1. En pocas palabras, cuando ambas entradas son "1" la salida será "1". Si aplicamos un "0" a la terminal 4 y mantenemos la entrada a la terminal 5 en "1", entonces la corriente eléctrica podrá fluír directamente a través del diodo D1 de la fuente de voltaje a la terminal 4 siguiendo la flecha simbólica del diodo D1, con lo cual el voltaje en la terminal 1 se desplomará al nivel de "tierra eléctrica", o sea a "0". Con esto, si la entrada en la terminal 4 es "0" y la entrada en la terminal 5 es "1", la salida será "0". Y lo mismo ocurrirá cuando la entrada en la terminal 4 sea "1" y la entrada en la terminal 5 sea "0". En pocas palabras, cuando una de las entradas es "0" la salida será "0". Y si ambas entradas son "0" la salida será "0". Esta es precisamente la acción de un AND.

La principal desventaja de utilizar únicamente diodos para implementar funciones lógicas es que no hay manera alguna de implementar la función NOT, los diodos no proporcionan manera alguna de poder invertir un "1" lógico convirtiéndolo en un "0", o viceversa. Por otro lado, como los diodos no proporcionan amplificación alguna (en el sentido eléctrico) de la potencia de la señal digital, la señal se va deteriorando rápidamente por las pérdidas cumulativas de voltaje a través de los diodos.

Fue precisamente la invención del transistor bipolar lo que abrió el camino para la miniaturización electrónica y la dramática reducción de costos que permitieron la construcción de circuitos lógicos cada vez más complejos a precios accesibles al consumidor general. En su esencia más básica el transistor, además de su capacidad para poder amplificar señales analógicas tales como señales de audio y video cuyos voltajes pueden tomar cualquier valor dentro de ciertos rangos, tenía inherentemente la capacidad para poder actuar como un inversor lógico, esto es, como un bloque NOT:

En este diagrama esquemático, podemos ver que si aplicamos un voltaje Vin de +5 volts a la base del transistor, el transistor se "encenderá" conduciendo corriente eléctrica, y al hacer tal cosa el transistor se comportará como un "corto circuito" con lo cual el voltaje Vout entre sus otras dos terminales, el colector (la terminal superior) y el emisor (la terminal inferior) será prácticamente de cero. Si el interruptor eléctrico a la izquierda del circuito es bajado de modo tal que a la base del transistor ya no le llegue ningún voltaje, entonces el transistor se comportará como un circuito "abierto", y el voltaje de salida Vout será el mismo que hay entre su colector y su emisor, o sea +5 volts. Si designamos al voltaje de +5 volts como un "1" lógico y al voltaje de cero volts como un "0" lógico, lo que tenemos en esencia es un circuito que con un "1" a la entrada nos produce un "0" a la salida, y con un "0" a la entrada nos produce un "1" a la salida. Esta es precisamente la acción de un inversor NOT. Con la adición de algunos cuantos componentes adicionales, podemos irle agregando al transistor básico más terminales de entrada con las cuales podemos construír otros bloques lógicos, además de proporcionarle al diseño básico un funcionamiento eléctrico más estable que el que puede proporcionar el circuito anterior.

Tras la invención del transistor, con la invención del circuito integrado se abrió el camino hacia lo que prometió ser una miniturización aún más dramática de componentes electrónicos que prometía reducir enormemente el espacio ocupado por cualquier aparato electrónico, reducir enormemente el consumo de energía para poder tenerlo operando, y reducir el costo de los componentes usados para construír un equipo electrónico. Es así como empezaron a surgir diseños óptimos que por su simpleza y bajo costo comenzaron a utilizarse como "ladrillos" básicos para la integración a gran escala que estaba por llegar. Las familias lógicas de circuitos integrados en un principio fueron identificadas casi todas ellas por tres letras como RTL, TTL, DTL, MOS; o por cuatro letras como DCTL y CMOS, una costumbre que todavía prevalece hasta nuestros días. A continuación tenemos un resumen de lo que hay detrás de estos acrónimos.

La lógica DTL (Diode-Transistor-Logic)

Aquí el diseño básico está centralizado en torno a un transistor bipolar en cuya entrada se han añadido varios diodos, como lo muestra el siguiente diagrama esquemático:

La forma en la que trabaja este circuito es la siguiente: supóngase que todas las tres entradas A, B y C están conectadas al nivel de voltaje alto (en este caso, Vcc), que identificaremos aquí de la manera usual como un "1" lógico. Siendo así, habrá una señal de entrada en la base del transistor que ocasionará que dicho transistor conduzca corriente eléctrica, lo cual hará que la salida del transistor caiga prácticamente al nivel de "0". Ahora bien, si cualquiera de las tres entradas A, B y C recibe una señal de "0", o sea si cualquiera de los diodos a la entrada es "aterrizado" a tierra eléctrica con una señal de "cero", el voltaje a la entrada de la base del transistor será prácticamente de cero, con lo cual el transistor no conducirá corriente eléctrica alguna y por lo tanto el voltaje de salida del mismo será igual a Vcc o a "1". Este comportamiento lo podemos resumir de la manera siguiente: si cualquiera de las entradas A, B ó C toma un valor de "0", la salida será "1". Unicamente cuando todas las entradas tienen un valor de "0" podremos tener una salida de "0". Si recordamos bien lo que vimos en los capítulos anteriores, esta es precisamente la función NAND, como lo indica la función Boleana puesta a la derecha a la salida del colector del transistor. Es así como el bloque fundamental de la lógica DTL viene siendo precisamente la función NAND.

La lógica DCTL (Direct-Coupled Transistor Logic)

A diferencia del diseño anterior que requiere un diodo para implementar cada entrada, la lógica DCTL requiere del uso de un transistor para implementar cada entrada de la compuerta lógica, lo cual naturalmente aumenta el costo y la complejidad del circuito. El diagrama esquemático para el componente esencial de esta clase de lógica es el siguiente:

La forma en la cual trabaja este circuito es la siguiente: supóngase que ambas entradas A y B no están recibiendo voltaje alguno, estando ambas conectadas a "tierra eléctrica" (que viene siendo el equivalente de una señal de "cero"). En tal caso, ninguno de los dos transistores estará conduciendo corriente eléctrica alguna, y la salida será igual al voltaje Vcc, o sea un "1" lógico. Si aplicamos un voltaje a cualquiera de los dos transistores (o sea una señal de "1") o a ambos, entonces la salida unida de ambos colectores caerá a un voltaje prácticamente de cero. Puesto de otra manera, si cualquiera de las dos entradas A y/o B toma un valor de "uno", la salida caerá a "cero". Se requiere que ambas entradas sean "0" para que la salida sea "1". Esta es precisamente la función lógica NOR, como lo indica la expresión Boleana puesta a la derecha a la salida conjunta de los colectores de ambos transistores.

La lógica RTL (Resistor-Transistor-Logic)

Esta clase de circuitos integrados fue la primera que proporcionó en el mercado componentes lógicos discretos a bajo costo con los cuales se empezaron a implementar muchas funciones lógicas básicas. Aunque todavía no había alguna "estandarización" llevada a cabo por las empresas que iniciaron la fabricación de circuitos integrados RTL, por vez primera se empezaron a fabricar muchos tipos de circuitos que además de funciones lógicas básicas implementaban algunas funciones algo más sofisticadas, como contadores binarios o registros de transferencia.

Por la forma en la cual está integrada la electrónica interna, el "bloque fundamental" de la familia RTL no es ninguna de nuestras funciones lógicas básicas (OR, AND, NOT), sino la función NOR. El bloque NOR es el "caballito de batalla" de la familia RTL.

Los circuitos integrados RTL siempre se destacaron por ser una familia de componentes muy resistentes a cualquier tipo de falla. Inclusive en la literatura promocional de los mismos se afirmaba que no había forma posible de dañarlos aunque al construír un prototipo usando circuitos RTL se cometiesen errores al hacer las conexiones eléctricas. Quizá uno de los libros que más contribuyeron a popularizar el uso de los circuitos integrados de la familia RTL fue el libro "RTL Cookbook" de Don Lancaster, un personaje tan pintoresco como prolífico que tuvo la virtud de hacer accesibles en sus libros conocimientos que anteriormente sólo estaban al alcance de estudiantes de la carrera de ingeniería eléctrica en universidades de prestigio.

Entre algunos de los circuitos integrados construídos con tecnología RTL podemos mencionar como ejemplos los siguientes, construídos por la empresa Motorola:

MC789P -- Hex inverter (seis inversores NOT)Además de estos componentes podemos mencionar el ul914 (Dual two input NOR, dos NOR de dos entradas) construído por varios fabricantes.

MC724P -- Quad two input gate (cuatro NORs de dos entradas)

MC790P -- Dual J-K Flip-Flop (dos flip-flops J-K)

Para quienes tienen nociones básicas de electrónica elemental, a continuación se reproduce el diagrama esquemático que muestra la manera en la cual opera un circuito RTL esencial, un NOR de tres entradas A, B y C, en cuya construcción se utilizan tres transistores y cuatro resistencias:

La forma en la que trabaja este circuito es la siguiente: cuando las tres entradas están "aterrizadas a tierra" (el símbolo que aparece en la parte más inferior del diagrama), lo cual equivale a un cero (0) lógico, los tres transistores permanecen desactivados, no conducen ninuna corriente, con lo cual a la salida de los mismos será igual al voltaje Vcc que equivale al uno (1) lógico. En otras palabras, cuando todas las entradas son (0), la salida es (1). Pero cuando una de las entradas A, B o C recibe un voltaje, un (1), entonces el transistor al cual le llega la señal empieza a conducir, con lo cual se desploma el voltaje de salida. En otras palabras, si cualquiera de las entradas tiene un valor de (1), la salida caerá a (0). La salida será (1) únicamente cuando todas las entradas sean (0). Esta es precisamente la función NOR.

La familia RTL quedó descontinuada del mercado cuando hizo su aparición una nueva familia de circuitos integrados basada en otra tecnología que veremos a continuación.

La familia TTL (Transistor-Transistor-Logic)

Aquí podemos hablar ya de toda una verdadera familia de circuitos lógicos basada en la tecnología TTL, la cual fue creada por la compañía Texas Instruments (la misma compañía que dió el primer impulso fuerte al desarrollo de los circuitos con un nivel elevado de integración)

Por la forma en la cual está integrada la electrónica interna, el "bloque fundamental" de la familia TTL tampoco es ninguna de nuestras funciones lógicas básicas (OR, AND, NOT), sino la función NAND, lo cual se concluye al apreciar el diagrama esquemático del siguiente circuito TTL de dos entradas:

El par de transistores mostrados en el lado derecho del diagrama esquemático en conjunto recibe el nombre de configuración totem-pole, a semejanza de los totems indios, y actúan como par inseparable para proporcionar la eficiencia máxima de velocidad que es característica de la familia TTL. Como puede apreciarse en el transistor de entrada, este es un transistor especial de dos colectores que requiere un proceso más cuidadoso de fabricación. Cuando se ensambla un circuito de esta naturaleza a través de componentes individuales discretos, es frecuente agregarle un diodo entre los dos transistores que forman el conjunto totem-pole que ayuda a impedir que los transistores a la salida conduzcan simultáneamente:

WINDOWS XP ES INMORTAL Y CONTROLA EL 96% DEL MERCADO DE NETBOOKS.

El mundo de los netbooks está convulsionado al borde de la división, algunas cosas se mantienen como en el principio; al menos por el momento. Tal es el caso del dominio de Windows XP sobre este mercado.

El sistema operativo inmortal se encontraría en el 96% de los netbooks de acuerdo a un estudio realizado por la firma NPD. Esto implicaría un crecimiento exponencial en la tasa de participación del SO de Redmond en perjuicio de la cuota de las distintas distribuciones de linux.

Además, según algunos blogueros como Brandon Leblanc, uno de los principales contribuyentes al éxito de Windows XP son las distribuciones de Linux, ya que los menores costos de estos equipos (por el ahorro en licencias) ha redundado en buenas ventas, pero cuando los usuarios prueban linux no tienen la misma calidad de experiencia, se cansan o frustran y los devuelven.

En lo personal, creo que algo de razón puede tener por cuanto muchos usuarios compran netbooks equipados con distribuciones de linux sin saber que están comprando y sin querer experimentar; buscan usarlo con naturalidad inmediatamente como un portátil común y corriente, pero pequeño y más limitado.

Finalmente, por ahora nos queda por ver que ocurrirá ahora que comenzaran a salir netbooks con otras opciones como Android.